Задача 1.

Заполнить таблицу истинности (a-h) для соответствующих варианту схем.

Команда 1,5 - схема 1

Команда 2,6 - схема 2

Команда 3,7 - схема 3

Команда 4,8,9 - схема 4

Задача 2.

А) Записать таблицу истинности для указанной схемы.

Б) Зарисовать аналогичную схему, использую абстрактные модели логических элементов (см. задачу 1)

Задача 3.

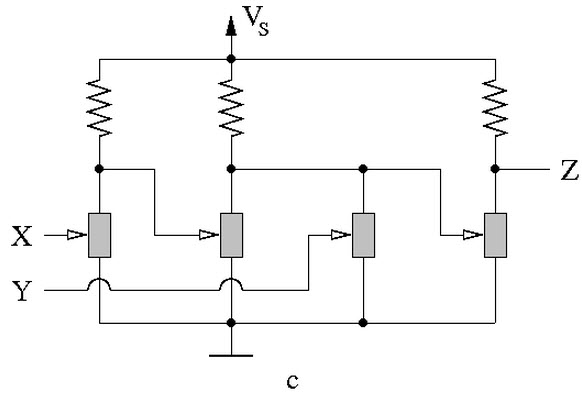

Каждый транзистор имеет пороговое напряжение V_T = 2В и сопротивление (при включении) R_ON = 1 кОм. Предположим,

Команда 1 - V_S = 3.0 и R1 = R2 = 12000.0Ω.

Команда 2 - V_S = 3.5 и R1 = R2 = 4200.0Ω.

Команда 3 - V_S = 4.0 и R1 = R2 = 24200.0Ω.

Команда 4 - V_S = 4.5 и R1 = R2 = 14400.0Ω.

Команда 5 - V_S = 5.0 и R1 = R2 = 6700.0Ω.

Команда 6 - V_S = 5.5 и R1 = R2 = 21900.0Ω.

Команда 7 - V_S = 6.0 и R1 = R2 = 8700.0Ω.

Команда 8 - V_S = 6.5 и R1 = R2 = 3500.0Ω.

Команда 9 - V_S = 7.0 и R1 = R2 = 16800.0Ω.

Каково максимальное потребление мощности (в Вт) этой схемы?

Подсказка: 1) Составьте таблицу истинности и посмотрите какие транзисторы включены, а какие - нет. 2) Включенные транзисторы меняем на резисторы с сопротивлением R_ON, выключенные исключаем из схемы и находим эквивалентное сопротивление сети резисторов. 3) Зная сопротивление всей схемы и напряжение питания V_S, просчитываем мощность каждого из вариантов таблицы истинности и указываем в ответе максимальное значение.

Задача 4.

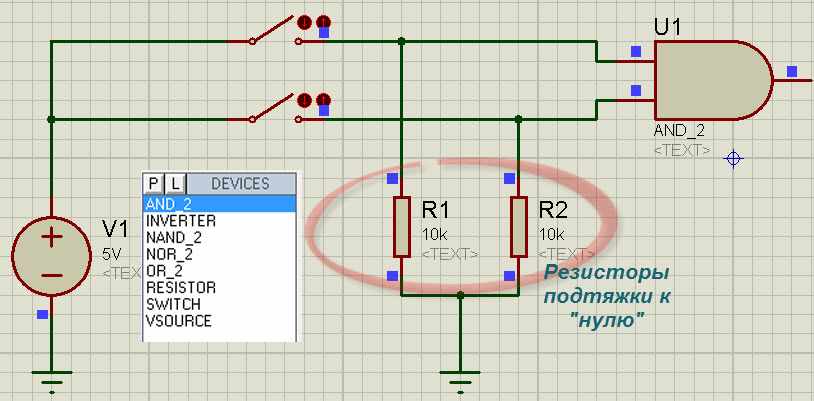

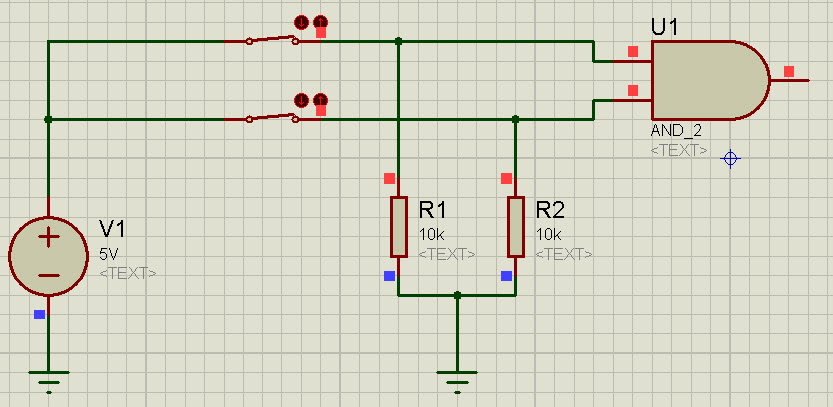

Открываем Proteus.

Ваша целью в этой задаче является разработка схемы логического элемента с 3 входами, реализующего операцию соответствующего варианта (например, Z = ¬ (С*(А + В)), где символ ¬ обозначает логическое отрицание (инверсию)).

Команда 1,4,7: Z=¬(А*¬В+¬С))

Команда 2,5,8: Z=(С+¬(А*В))

Команда 3,6,9: Z=¬(С*(А+В))

С каждой команды - скриншоты в электронном виде (8 шт, по таблице истинности) с синими (лог. "0") и красными (лог. "1") квадратиками, как в примере.

Подсказка:1) составьте таблицу истинности; 2) подберите элементы; 3) реализовывайте в Proteus.

Пример (увеличиваем через правую кнопку мыши -> Открыть рисунок в новом окне):

Вместо элемента "И", вставляйте свою "логику", ну и третий вход по аналогии .

Резисторы "подтяжки" используются для определенности входов логического элемента. В случае её отсутствия, когда ключ не замкнут, состояние входов не определено (или диктуется космическими силами инопланетян :), в виде наводок на входы). Таким образом, когда ключ не замкнут входы лог.элемента "притянуты" к "земле" (лог. "0", синий квадрат). Как только ключ замыкается, ток идет по пути наименьшего сопротивления, т.е. ко входам лог.элемента.

Ключи в схеме интерактивные, т.е. ими можно управлять (мышкой) во время симуляции.

Удачи!